Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405 Commercial Off-The-Shelf Airborne Electronic Hardware Assurance Methods—Phase 3— Embedded Controllers

November 2017

**Final Report**

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

U.S. Department of Transportation Federal Aviation Administration

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              | Technical Report Documentation Page                                                                                                                                                                                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1. Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2. Government Accession No   |                                                                                                                                                                                                                                                      |  |

| DOT/FAA/TC-17/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                                                                                                                                                                                                                                                      |  |

| 4. Title and Subtitle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5. Report Date               |                                                                                                                                                                                                                                                      |  |

| COMMERCIAL OFF-THE-SHEL<br>ASSURANCE METHODS – PHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C HARDWARE November 2017     |                                                                                                                                                                                                                                                      |  |

| EMBEDDED CONTROLLERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              | 6. Performing Organization Code                                                                                                                                                                                                                      |  |

| 7. Author(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              | 8. Performing Organization Report No.                                                                                                                                                                                                                |  |

| Laurence H. Mutuel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D8                           |                                                                                                                                                                                                                                                      |  |

| 9. Performing Organization Name and Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              | 10. Work Unit No. (TRAIS)                                                                                                                                                                                                                            |  |

| Thales Air Traffic Management U.S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S.                           |                                                                                                                                                                                                                                                      |  |

| 10950 El Monte Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              | 11. Contract or Grant No.                                                                                                                                                                                                                            |  |

| Overland Park, Kansas 66211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                                                                                                                                                                                                                                                      |  |

| 12. Sponsoring Agency Name and Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              | 13. Type of Report and Period Covered                                                                                                                                                                                                                |  |

| U.S. Department of Transportation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              | Final Report                                                                                                                                                                                                                                         |  |

| Federal Aviation Administration<br>950 L'Enfant Plaza SW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              | 14. Sponsoring Agency Code                                                                                                                                                                                                                           |  |

| Washington, DC 20024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              | AIR-134                                                                                                                                                                                                                                              |  |

| 15. Supplementary Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ical Center Aviation Researc | h Division Technical Monitor was Manny Rios.                                                                                                                                                                                                         |  |

| 16. Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |                                                                                                                                                                                                                                                      |  |

| This report provides information on assurance methods for commercial off-the-shelf (COTS) airborne electronic hardware (AEH) embedding microcontrollers. These methods address the safe operations aspects of certification and contribute to the development of a comprehensive framework for COTS assurance. This research highlights the current use of microcontrollers in AEH and the trends for the near future, and describes the challenges related to safety.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |                                                                                                                                                                                                                                                      |  |

| Microcontrollers cover a large spectrum of devices, which complicates the definition of an overarching method to determine the applicability of assurance methods. The current classification is primarily driven by the microcontrollers' manufacturers and therefore focuses on hardware characteristics that may or may not impact the ability to perform a safety assessment in a manner consistent with the system-level assessment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |                                                                                                                                                                                                                                                      |  |

| The proposed safety assurance process follows the steps of system safety assurance, which is the most applicable, given that COTS microcontrollers embed both software and hardware functions. These steps include the identification of failure modes, the determination of their effects given an intended use at system level and usage domain at component level, the classification of these effects, and the recommendation of mitigation techniques. As these components are COTS, their design may or may not include built-in mitigation techniques. The last step is to assess the effectiveness of the built-in mitigations and recommend additional ones as needed to meet the safety objectives. Existing guidance documents for assurance at system-level, software, and hardware-levels, and regulatory material are reviewed for applicability. Tailoring is recommended to better cover COTS microcontrollers. |                              |                                                                                                                                                                                                                                                      |  |

| The approach is to target the main objectives of a structured development process (i.e., ensuring the correct functional performance under all foreseeable conditions with no anomalous behavior). The aim is to return to certification basics of 14 CFR (i.e., 14 CFR 23/25/27/29.1301 and 23/25/27/29.1309): intended functions that are fit-for-purpose, proper, and safe functioning within aircraft operating conditions, and technical suitability supporting continued airworthiness.                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |                                                                                                                                                                                                                                                      |  |

| 17. Key Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              | 18. Distribution Statement                                                                                                                                                                                                                           |  |

| COTS, Embedded controller, Microcontroller, assurance, Failure<br>mode, ECC, AEH, Redundancy, Fault injection, Safety process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              | This document is available to the U.S. public through the National Technical Information Service (NTIS), Springfield, Virginia 22161. This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at |  |

|                                        | actlibrary.tc.faa.gov.               |                  |           |

|----------------------------------------|--------------------------------------|------------------|-----------|

| 19. Security Classif. (of this report) | 20. Security Classif. (of this page) | 21. No. of Pages | 22. Price |

| Unclassified                           | Unclassified                         | 49               |           |

Form DOT F 1700.7 (8-72)

Reproduction of completed page authorized

## ACKNOWLEDGEMENTS

This research has been coordinated with technical experts and reviewers at Thales Avionics SAS by Cyril Marchand. Didier Regis and Guy Berthon acted as internal reviewers for this report.

Page

| EXEC | CUTIVI     | E SUMN                                             | MARY                                                                                                                                                                              | Х                                    |

|------|------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1.   | INTR       | ODUC                                               | ΓΙΟΝ                                                                                                                                                                              | 1                                    |

|      | 1.1<br>1.2 | Backg<br>Purpo                                     |                                                                                                                                                                                   | 1<br>2                               |

| 2.   | IDEN       | TIFICA                                             | TION OF EMBEDDED CONTROLLERS FOR AEH PURPOSES                                                                                                                                     | 3                                    |

|      | 2.1        | Chara                                              | cteristics of Embedded Controllers                                                                                                                                                | 3                                    |

|      |            | 2.1.1<br>2.1.2                                     | Definition and Architectures<br>Microcontrollers Families                                                                                                                         | 3<br>6                               |

|      | 2.2        | Criter                                             | ia Used For Categorizing Microcontrollers                                                                                                                                         | 6                                    |

|      | 2.3        | 2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8 | Complexity<br>Criticality<br>End-User Accessibility<br>Instruction Type or Set<br>Instruction Storage<br>Memory Architecture                                                      | 6<br>7<br>8<br>8<br>9<br>9<br>9<br>9 |

|      |            |                                                    | Current Usage<br>Foreseen Future Usage                                                                                                                                            | 10<br>10                             |

| 3.   |            | RED EV<br>FROLL                                    | ENTS AND FAILURE MODES OF EMBEDDED<br>ERS                                                                                                                                         | 11                                   |

|      | 3.1<br>3.2 |                                                    | l Fault Classification<br>Identified with COTS microcontrollers                                                                                                                   | 12<br>12                             |

|      |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | Issues with Derating<br>Sparing Reliability<br>Embedded Controllers for Flash NAND Memories<br>Handling of Errata<br>Intellectual Property<br>Spectrum of Microcontroller Devices | 13<br>13<br>13<br>14<br>14<br>14     |

|    | 3.3<br>3.4        | Generic Failure Modes at Logical Level for COTS PRODUCTS<br>Fault Model at Physical and Logical Abstraction Levels                                                                                                                          | 15<br>15             |  |  |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

|    |                   | <ul><li>3.4.1 Identification of Failure</li><li>3.4.2 Major Findings for Fault Models at Logic and RTL Levels</li></ul>                                                                                                                     | 15<br>16             |  |  |

| 4. | MITI              | IGATION TECHNIQUES FOR EMBEDDED CONTROLLERS                                                                                                                                                                                                 | 17                   |  |  |

|    | 4.1<br>4.2<br>4.3 | Summary of Effects of Hardware Faults<br>Summary of Effects of Software Faults<br>Overview of Built-in Mitigation in Microcontrollers                                                                                                       | 17<br>18<br>19       |  |  |

|    |                   | <ul><li>4.3.1 Memory Management Unit</li><li>4.3.2 Control Flow Checking</li></ul>                                                                                                                                                          | 19<br>20             |  |  |

|    | 4.4               | Description of Issues with Built-in Mitigation Techniques                                                                                                                                                                                   | 21                   |  |  |

|    |                   | <ul><li>4.4.1 Accessibility</li><li>4.4.2 Management of Errata</li></ul>                                                                                                                                                                    | 21<br>21             |  |  |

|    | 4.5               | Identification of Potential Additional Mitigation                                                                                                                                                                                           | 21                   |  |  |

| 5. | REC               | RECOMMENDATIONS ON ASSURANCE PROCESSES                                                                                                                                                                                                      |                      |  |  |

|    | 5.1               | Applicability of Existing Standards and Guidance                                                                                                                                                                                            | 22                   |  |  |

|    |                   | <ul> <li>5.1.1 Applicability of Hardware and Software Assurance Standards</li> <li>5.1.2 Applicability of System Safety Standards</li> <li>5.1.3 Details Within EASA CM SWCEH-001</li> <li>5.1.4 Current Practices</li> </ul>               | 22<br>22<br>23<br>25 |  |  |

|    | 5.2               | Applicability of Safety Analyses                                                                                                                                                                                                            | 25                   |  |  |

|    |                   | <ul><li>5.2.1 Fault Tree Analysis</li><li>5.2.2 Failure Mode and Effect Analysis</li><li>5.2.3 Link With Usage Domain Analysis</li></ul>                                                                                                    | 25<br>26<br>26       |  |  |

|    | 5.3               | Issues to Track for Assurance Process                                                                                                                                                                                                       | 26                   |  |  |

|    |                   | <ul> <li>5.3.1 Availability of Documentation</li> <li>5.3.2 Robustness Verification (Fault Injection)</li> <li>5.3.3 In-Use Validation (Testing in General)</li> <li>5.3.4 Assurance of Software Code and Qualification of Tools</li> </ul> | 27<br>27<br>27<br>28 |  |  |

|    | 5.4               | Summary of Findings and Recommendations                                                                                                                                                                                                     | 28                   |  |  |

|    |                   | 5.4.1 Classification of COTS Microcontrollers                                                                                                                                                                                               | 28                   |  |  |

| 5.4.2     | Analyzing a Device for Usage Domain                   | 28 |

|-----------|-------------------------------------------------------|----|

| 5.4.3     | Application of Assurance Processes                    | 29 |

| 5.4.4     | Obtaining COTS Microcontroller Data and Documentation | 30 |

| 5.4.5     | Means of Compliance                                   | 31 |

| REFERENCE | es                                                    | 33 |

## APPENDICES

7.

A—GLOSSARY

# LIST OF FIGURES

| Figure |                                                                | Page |

|--------|----------------------------------------------------------------|------|

| 1      | Block Diagram of Generic Microcontroller                       | 4    |

| 2      | Block Diagram of Freescale MPC7447A Standalone Core Processing | 5    |

| 3      | Block Diagram of Freescale MPC8610 Integrated Host Processor   | 6    |

# LIST OF TABLES

| Table | F                                                                              | Page |

|-------|--------------------------------------------------------------------------------|------|

| 1     | Relation between Microcontroller Failure Modes and Commonly Used Failure Modes | 15   |

# LIST OF ABBREVATIONS AND ACRONYMS

| A/D    | Analog to digital                                                 |

|--------|-------------------------------------------------------------------|

| AEH    | Airborne electronic hardware                                      |

| AFE    | Authority for Expenditure                                         |

| ALU    | Arithmetic logic unit                                             |

| BIT    | Built-in test                                                     |

| CFC    | Control flow checking                                             |

| CISC   | Complex instruction set computer                                  |

| COTS   | Commercial off-the-shelf                                          |

| CPU    | Central processing unit                                           |

| D/A    | Digital to analog                                                 |

| DAL    | Development assurance level                                       |

| DMA    | Direct memory access                                              |

| EASA   | European Aviation Safety Agency                                   |

| ECC    | Error correcting code                                             |

| FHA    | Functional Hazard Assessment                                      |

| FMEA   | Failure mode and effects analysis                                 |

| FTA    | Fault tree analysis                                               |

| I2BCFC | Intra-inter block control flow checking                           |

| IDAL   | Item development assurance level                                  |

| IP     | Intellectual property                                             |

| MMU    | Memory management unit                                            |

| NAND   | Not-AND                                                           |

| OS     | Operating system                                                  |

| RAM    | Random access memory                                              |

| RISC   | Reduced instruction set computer                                  |

| ROM    | Read-only memory                                                  |

| RTCA   | Radio Technical Commission for Aeronautics                        |

| RTL    | Register transfer level                                           |

| SDS    | Software and Digital Systems                                      |

| SPI    | Serial peripheral interface                                       |

| SRAM   | Static random access memory                                       |

| SWTES  | Software-based error detection technique using encoded signatures |

| UART   | Universal Asynchronous Receiver/Transmitter                       |

| VeTeSS | Verification and Testing to Support Functional Safety Standards   |

### EXECUTIVE SUMMARY

This report is part of a research thrust on commercial off-the-shelf (COTS) airborne electronic hardware (AEH) assurance methods that addresses the "safe operation" aspect of certification and promotes the development of a comprehensive framework for COTS assurance. This framework covers:

- The understanding of current and foreseen future uses of COTS in AEH.

- The description of related safety issues and concerns.

- The documentation of failure modes and their relevance to an AEH context.

- The investigation of existing mitigation techniques and their effectiveness.

- The development of objective criteria for determining the effectiveness of safety.

- The determination of airworthiness assurance methods for AEH integrating the COTS under consideration.

This report applies the above focus points to embedded controllers (also called COTS microcontrollers). It also initiates the process of investigating the shortcomings of current assurance methods and the potential for remedies. Applicable assurance methods include system-level guidelines within SAE/ARP4754A and SAE/ARP4761, software-level guidance in RTCA/DO-178C, and hardware-level guidance in RTCA/DO-254. Other assurance standards exist in other domains, particularly for road vehicle safety in ISO 26262, that recommend assurance processes applicable to microcontrollers.

Microcontrollers cover a large spectrum of devices; this complicates the definition of an overarching method to determine how to apply assurance methods and which ones are applicable. Currently, the classification schemes are mostly based on hardware-related characteristics that may or may not impact the ability to perform a safety assessment in a manner consistent with the system-level assessment.

This report focuses on microcontrollers embedded within COTS products, not only executing software but also providing so-called peripheral hardware functions. This distinction eliminates COTS controllers (i.e., not able to execute application software) and core processors alone (i.e., not providing peripheral hardware functions other than those necessary for interfacing outside the device, such as memory access controllers). Because of both technology capability and performance needs, the current trend is moving toward highly integrated core processors that embed on the same die the potentially multiple core processing, memories, and peripherals.

Microcontroller manufacturers categorize their devices primarily by their technical performance in terms of number of hardware functions, core processing power capabilities, and other physical characteristics, such as electrical power consumption. However, the certification community using DO-254-based classification criteria addresses hardware characteristics as they relate to the notion of complexity; unfortunately, the notion of complexity inevitably suggests multiple interpretations. EASA certification memorandum SWCEH-001 further introduced the category of the highly complex microcontroller based on criteria related to the internal architecture of a device. This introduction further increased the range of interpretative material that would be required to determine an acceptable path to certification compliance. Beyond the mere assessment of COTS microcontrollers' characteristics, the relationship with the objectives of the developmentassurance process would require clarification.

Therefore, the approach is to target the main objectives of a structured development process (i.e., ensuring the correct functional performance under all foreseeable conditions with no anomalous behavior). The aim is to return to certification basics of 14 CFR (i.e., 14 CFR 23/25/27/29.1301 and 23/25/27/29.1309): intended functions that are fit-for-purpose, proper and safe functioning within aircraft operating conditions, and technical suitability supporting continued airworthiness. System-level safety assessments are then applicable to identify microcontrollers' failure modes, analyze and classify their effects according to the applicable classification scheme (e.g., per AC 25.1309), and evaluate existing failure mitigations.

The automobile industry provides most of the verification results from fault injection in microcontrollers. The fault testing is performed at physical and logical levels, but rarely at the functional level at which the intended use is attached. The results indicate that most faults in microcontrollers manifest as bit-flips, justifying the most common mitigation technique to be error detection and correcting codes. Memory management units provide wider fault detection and recovery and are more and more embedded in microcontrollers. However, with respect to AEH for COTS in general and for complex or highly complex COTS microcontrollers in particular, design data are not available, at least to the level necessary to provide sufficient development assurance commensurate with the expected usage.

This report provides recommendations for assurance process for COTS microcontrollers. An apriori classification could be determined by (1) taking into account the criticality (from the allocated development assurance level), and (2) on the basis of an assessment of both the device characteristics and its target usage domain. The notion of independence between the processing core (performing purely software functions) and the other peripheral hardware functions can inform on the potential applicability and scope of system-level safety assurance combined with software-level assurance (when independence claim cannot be formally justified), or hardwarelevel assurance only (with justified independence claims). In other words, the challenge is to discern among miscellaneous considerations, whether or not a COTS microcontroller can be assured at system-level, possibly with the help of software, and, if not, how hardware-level assurance only can be achieved. In the latter case, collecting all available artifacts in a structured manner could provide acceptable assurance. For example, the definition and analysis of a device's usage domain, together with its validation and verification, could allow a COTS microcontroller classified as complex or highly complex under current criteria to still be shown as mastered in terms of both adequate functioning and safe operation. For highly complex microcontrollers with allocated development assurance levels of A or B, additional assessments of potential dysfunctional behavior should be performed. Finally, the issue of documentation to support the required artifacts is no different from other COTS devices. The recommendation is to integrate the information from the available COTS artifacts into the development process to perform to the largest extent possible the traditional activities of a requirements-based approach (e.g., requirements capture, requirements validation, design data production, consistency of the overall process via traceability, implementation within the surrounding AEH, and performing requirements-based verification).

## 1. INTRODUCTION

## 1.1 BACKGROUND

Commercial off-the-shelf (COTS) items are increasingly penetrating into both the commercial and the military segments of the aerospace market. Radio Technical Commission for Aeronautics (RTCA) standards, namely DO-254 "Design Assurance Guidance for Airborne Electronic Hardware" [1] and DO-178C "Software Considerations in Airborne Systems and Equipment Certification" [2], were developed with the issue of COTS assurance in mind. However, they did not recommend specific methods or objective criteria for safety assurance and airworthiness.

In a general context of airworthiness, the focus is threefold:

- Intended function (14 CFR 23.1301, 25.1301, 27.1301, and 29.1301)—Component selection from a functional standpoint and design to meet the function contribute to this aspect.

- Operating conditions (14 CFR 23.1309, 25.1309, 27.1309, and 29.1309)—Component selection from the point of view of characteristics and performance and environmental qualification of these components contribute to this aspect.

- Safe operation (14 CFR 23.1309, 25.1309, 27.1309, and 29.1309)—Failure modes and failure mitigation of the selected components contribute to this aspect [3–6]. Reliability considerations are integrated in the demonstration of achievement of safe operation.

The research thrust on COTS airborne electronic hardware (AEH) assurance methods addresses safe operation and supports the development of a comprehensive framework for COTS assurance. The framework includes:

- The understanding of current and foreseen future use of COTS in AEH.

- The description of safety issues and concerns.

- The documentation of failure modes for these COTS and the relevance to AEH context.

- The investigation of existing mitigation techniques and their effectiveness.

- The development of objective criteria for determining the effectiveness of safety.

- The determination of airworthiness assurance methods for AEH integrating the COTS under consideration.

Previous research under Authority for Expenditure (AFE) Project 75 (COTS AEH Assurance Methods) documented 22 COTS issues and proposed a structure to address future COTS AEH assurance standards [7–10]. Continuation of the research on the identified issues with COTS is currently allocated in part to a supplement to AFE Project 75 and to a phase 3 research task order under the Software and Digital Systems (SDS) Program, which focuses on commodity memories and embedded controllers [11]. This report is produced under the SDS Program and pertains to embedded controllers. Note that in the process of describing the COTS embedded controllers in AEH, considerations of intended function and operating conditions are integrated in the discussion.

## 1.2 PURPOSE

This report is the second on the SDS research and addresses embedded controllers (also called microcontrollers). This report informs on applicability of safety assurance processes based on the characteristics of microcontrollers, their fault models, and mitigation means.<sup>1</sup> More specifically, the following topics are covered:

- The identification of the various types of embedded controllers that are being used and might be used in the near future by aerospace equipment manufacturers

- The definition of categories for embedded controllers based on their characteristics

- The identification of methods to categorize a given device into one of the defined categories

- The description of the types of embedded controllers failure modes

- The identification of issues and adequacy associated with the embedded controllers' builtin fault mitigation techniques for the above failure modes (if any)

- The identification of additional potential internal and external fault mitigation techniques for the defined categories of embedded controllers

- The investigation of how embedded controllers could be integrated within system safety analyses (e.g., fault trees)

- The recommendation of software and AEH development assurance processes, including means of compliance

In the context of investigating assurance methods for embedded controllers, the focus is on COTS microcontrollers, which embed a processing core with software, as opposed to COTS controllers, which do not have a software function. Therefore, this report uses the term "microcontroller." Furthermore, the focus is on microcontrollers embedded within COTS products, executing not only protected code (from an intellectual property [IP] standpoint) but also providing hardware functions (e.g., memory controllers or input/output functions).

Section 2 of this report discusses the identification and classification schemes for microcontrollers. Section 3 describes the fault model of microcontrollers at different abstraction levels and lists identified issues with these COTS devices. Section 4 investigates the effects of faults in microcontrollers and the mitigation techniques. Section 5 focuses on the applicability of assurance processes, to include system, software, and hardware; this section also consolidates the findings and recommendations resulting from this research effort.

<sup>&</sup>lt;sup>1</sup> Disclaimer: In this report, COTS components for which the primary target is the consumer electronics market may be qualified as exhibiting a level of quality that is insufficient for AEH quality requirements, especially for safety-critical applications. This statement does not mean in any way that manufacturers may be lax or incompetent. What is meant is that manufacturing and supply processes that are perfectly rigorous and appropriate for the consumer electronics market may not meet requirements for AEH application, which require a mandatory level of assurance.

### 2. IDENTIFICATION OF EMBEDDED CONTROLLERS FOR AEH PURPOSES

This section provides the context information for executing the overarching tasks of a safety process: the identification and description of failure modes associated with embedded controllers, the assessment of their effects, and the determination of mitigation techniques.

The main challenge is related to the wide variety of embedded controllers, not only in terms of features but also in terms of intended functions. The objective of the following sections is to recommend a categorization scheme using characteristics that will be relevant in the context of safety assurance.

## 2.1 CHARACTERISTICS OF EMBEDDED CONTROLLERS

### 2.1.1 Definition and Architectures

An embedded controller is defined as a microprocessor-based system that is built to control a function or a range of functions that resides in a larger mechanical or electrical system. An embedded controller is also referred to as a microcontroller. This definition is coherent with the scope of this report to consider controllers embedded in a larger COTS product. However, the proposed scope is wider.

European Aviation Safety Agency (EASA's) definition of a COTS microcontroller is consistent with the generic definition above; the definition is more specific because it includes controllers that embed several hardware functions interacting with the processing core executable code. CM SWCEH-001 [12] defines a COTS microcontroller as any integrated circuit that executes software in a central processing unit (CPU) (processing core) and that implements peripheral hardware elements.

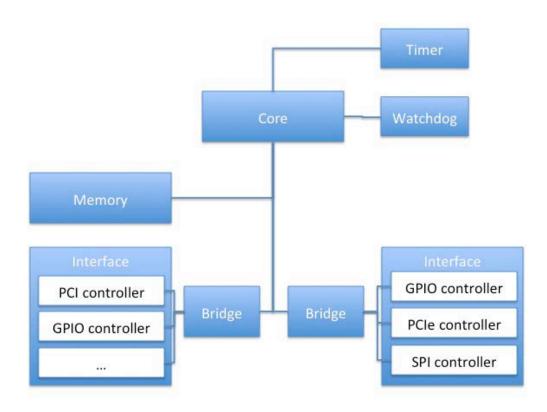

A generic microcontroller is described as a highly integrated component containing a single processing core, an internal memory, and programmable input/output peripheral interfaces and controllers (see figure 1).

Figure 1. Block diagram of generic microcontroller

This figure illustrates some of the most common peripheral interfaces: general-purpose input/output, serial peripheral interface (SPI), peripheral component interconnect, and express.

For a COTS product in general, the only available level of description is the one provided by its datasheet (e.g., block diagram, functional, and interface description), possibly complemented by additional data from the COTS supplier (e.g., users manuals and applications notes). This level is mainly a very first level of description (i.e., down to the strict necessary information for the user, at the system or software interface) to determine normal and proper functioning of the COTS to the desired behavior. For COTS microcontrollers in particular, the software interface is described through both the instruction set of the core processing portion and a set of control and status registers for the associated peripherals.

The assessment of failure modes and mitigation mechanisms requires a more dysfunctional than functional analysis, which can then only be performed at the COTS device level but is based on the available description of the architecture in terms of input, functional blocks diagram, and output. With those restrictions, the failure modes and mitigation mechanisms can only be assessed at this first level of description. In addition, failure rates and fault coverage figures can only be estimated, possibly with the help of the COTS device supplier but with inevitable assumptions, which might be difficult to validate.

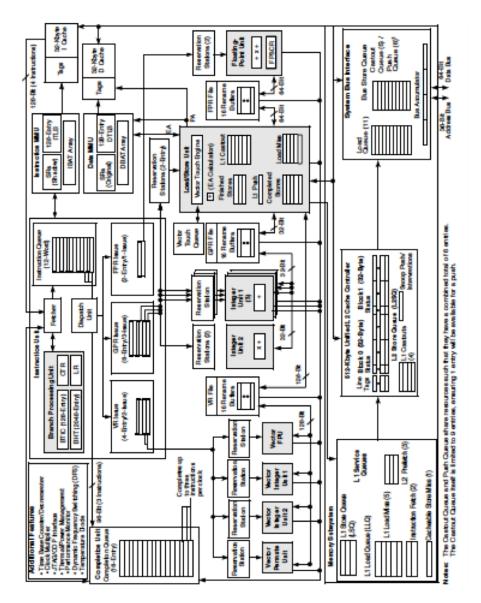

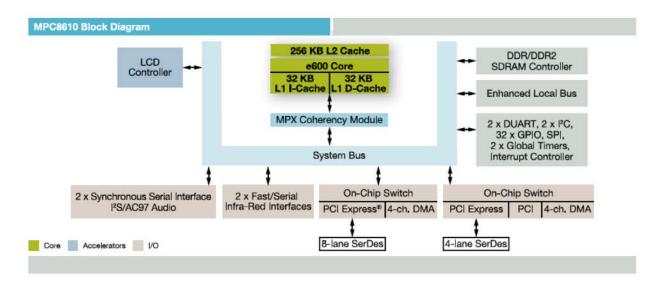

Consider specific instances to highlight the spectrum of embedded controllers. Figure 2 shows the block diagram of a MPC7447A, which is the fifth implementation of the fourth generation microprocessors from Freescale [13]. It is a standalone processing core. In comparison, figure 3 shows the block diagram of a MPC8610, which is an integrated processor: This single chip replaces four chips. All core-to-peripheral connections are integrated on the die [14].

Figure 2. Block diagram of Freescale MPC7447A standalone core processing

Figure 3. Block diagram of Freescale MPC8610 integrated host processor

The spectrum of available devices is significantly varied, and often the AEH designer and manufacturer need to work closely with the embedded controller supplier to ensure the availability of information that is required to support the development assurance processes.

## 2.1.2 Microcontrollers Families

The classification by family is provided as an example. It is specific to the microcontroller manufacturer and bears no impact on the assurance issue that is not covered by one or several of the criteria based on technical characteristics.

- Atmel<sup>®</sup> AVR<sup>®</sup> family tinyAVR<sup>®</sup>, megaAVR<sup>®</sup>, AVR XMEGA<sup>®</sup>

- PIC family PIC16F, PIC18F

- ARM family ARM7, ARM9, ARM11

- Intel 8051 family AT89s52, p89v51rd2

- Motorola 68HC11

## 2.2 CRITERIA USED FOR CATEGORIZING MICROCONTROLLERS

Categorization of COTS microcontrollers may be performed based on one or a combination of several of the criteria in this section. These criteria are currently being used, but they may not be relevant to the objective of integrating embedded controllers in the safety-assurance process. Section 5.4.1 discusses recommendations to remedy the classification issues related to complexity, criticality, and hardware-based criteria.

## 2.2.1 Functionality or Usage

This criterion pertains to whether the controller is dedicated to a specific function of a particular hardware or whether the controller is generic. Generic embedded controllers may perform the following tasks:

- Receiving and processing signals from controls (e.g., switches and buttons)

- Powering on and off

- Managing access control

- Managing thermal controls (e.g., fan control, CPU throttling, emergency shutdown in response to over-temperature condition)

- Controlling the indicator-light-emitting diodes

- Managing battery power and battery charging

- Allowing diagnostics and remote fault management

- Performing software-commanded reset

- Controlling the watchdog timer

This criterion is key to the safety-assurance process, regardless of whether the functionalities are performed by software, hardware, or both. However, it is rare for this criterion to drive the classification.

### 2.2.2 Complexity

This criterion allows for differentiating controllers that are simple sequencers, perform arithmetic logic, or are reconfigurable.

As a start, the following definitions are based on DO-254 and are used in the classification of microcontrollers:

- Simple electronic hardware—A hardware device is considered simple only if a comprehensive combination of deterministic tests and analyses appropriate to the development assurance level (DAL) /item development assurance level (IDAL) can ensure correct functional performance under all foreseeable operating conditions with no anomalous behavior.

- Complex electronic hardware All devices that are not simple are considered to be complex.

Note: An interpretation of the above definition for simple electronic hardware COTS is based on EASA CM SWCEH-001 and can be summarized as "the ability to verify by test on the physical device all requirements in all configurations, is a pre-requisite for a classification of a device as simple." [12]

A new category was introduced in EASA CM SWCEH-001 in addition to the DO-254 definitions for highly complex COTS microcontrollers. The definition invokes architectural specificities, such as number of cores, peripherals, or buses within the device. The practicality of such a definition may be questionable as the complexity gap is then highly dependent on the type of functionality provided by the COTS product and not on universally acceptable independent criteria. This might be the reason why only COTS microcontrollers will fall under this new category. As evolving technology will typically lead to an increase in complexity, other COTS products could eventually fall in that category. This classification has not been adopted by the FAA to date, the guidance for which is in reference [15], and the author of this report, as elaborated in section 5.4.1, instead recommends a classification that is less dependent on the microcontroller's functionality.

The EASA COTS-AEH report [16] and system-on-chip research report [17] considered microprocessors to be standalone complex COTS. Simple microcontrollers can be defined as microcontrollers implementing simple peripherals around their core processing.

Examples of simple interface peripherals include universal asynchronous receivers/transmitters, inter-integrated circuits, and SPIs. Examples of simple microcontrollers include Freescale MPC5567, the Texas Instrument C2000<sup>TM</sup> microcontroller series, or the older NXP LPC2119. Examples of complex microcontrollers include the Texas Instruments digital signal processor or Freescale MPC8610 (see figure 3).

Categorization by complexity is generally performed via an assessment of the COTS characteristics, which requires an adequate description of the COTS architecture down to an acceptable level of functional block identification, and with respect to one or several generally accepted criteria. Such criteria include the observable behavior of the various internal functions.

Categorization of COTS by complexity has always generated misunderstandings.

## 2.2.3 Criticality

Criticality, as reflected by the allocated DAL, is an input requirement flowed down from the system safety assessment. Although it cannot be modified, it is unlikely that compliance to the allocated DAL can be shown because the COTS design/development data may not be available.

#### 2.2.4 End-User Accessibility

This criterion specifically addresses whether the end user can modify the controller's instruction set or whether the user has access to the source code.

#### 2.2.5 Instruction Type or Set

This criterion presupposes end-user accessibility and focuses on whether the instruction set is complex instruction set computer (CISC) or reduced instruction set computer (RISC).

With CISC, the programmer can use one instruction in place of many simpler instructions. The RISC instruction set allows each instruction to operate on any register or to use any addressing mode and simultaneous access of program and data. RISC systems shorten execution time by reducing the clock cycles per instruction. CISC systems shorten execution time by reducing the number of instructions per program and having the hardware complete complex instructions.

The selection of instruction type or instruction set has no impact on the assurance issues (e.g., safety impact, intended function) that the classification would help address.

### 2.2.6 Instruction Storage

Embedded controllers typically have their own random access memory (RAM), independent from the memory for the main processing unit. The controller software may be stored in its own read-only memory (ROM).

This criterion allows for differentiating between controllers fetching instructions in an internal memory (i.e., embedded memory microcontroller) and controllers fetching instructions in an external memory (i.e., external memory microcontroller). Sub-criterion could consider the type: flash memory, electrically erasable programmable ROM, and static random access memory (SRAM).

The integration of memory units within the microcontroller implies that a large amount of computation by the core processing unit is hidden to the systems with which it interfaces.

An embedded microcontroller has all functional blocks on a chip: program, data memory, input/output ports, serial communication, counters, timers, and interrupts. An example of such structure is Intel<sup>®</sup> 8051.

An external memory microcontroller has no program memory on a chip. An example of such structure is Intel 8031.

This criterion plays a role in the assurance process, as instruction storage may be a source of issue. The following is an example: an embedded hardware controller that checks, or even corrects, a value during instruction fetching or RAM access.

#### 2.2.7 Memory Architecture

This criterion allows for distinguishing between Harvard memory architecture microcontrollers and Princeton memory architecture microcontrollers.

Harvard memory architecture microcontrollers have a dissimilar memory address space for the program and data memory in their processor. Princeton memory architecture microcontrollers have a common memory address for the program and the data memory in their processor.

#### 2.2.8 Internal Bus Width

This criterion classifies microcontrollers based on internal bus widths: 4 bits, 8 bits, 16 bits, or 32 bits.

In microcontrollers with 8-bit internal bus widths, the arithmetic logic unit (ALU) performs the arithmetic and logic operations at specific precision and performance. Examples of 8-bit microcontrollers are Intel 8031/8051, PIC1x, and Motorola MC68HC11 families.

Precision and performance are increased in microcontrollers with 16-bit internal bus widths compared with 8-bit microcontrollers. The timer can also be longer. Examples of 16-bit microcontrollers are Intel 8051XA and 8096, PIC2x, and Motorola MC68HC12 families.

Microcontrollers with 32-bit internal bus widths are typically used in automatically controlled devices, including implantable medical devices, engine/power control systems, office machines, and various appliances. Examples include Intel/Atmel 251 and PIC3x families.

This criterion primarily covers the performance aspects (precision and speed); although increased performance may allow for more critical applications, this particular criterion is qualified by the author and technical reviewers as having no impact on safety assurance issues. The usage criterion is retained instead for safety impacts.

## 2.3 USE OF MICROCONTROLLERS IN AEH

## 2.3.1 Current Usage

Microcontrollers are currently used in aircraft to perform the following functions:

- Receiving and processing signals from controls in the cockpit control panels

- Powering on and off in power distribution units (standalone or embedded in the chassis of avionics systems)

- Managing thermal controls (e.g., fan control, CPU throttling, emergency shutdown in response to over-temperature conditions) typically embedded in the avionics chassis

- Controlling the indicator-light-emitting diodes on faceplates and cockpit panels

- Managing battery power and battery charging

- Controlling the watchdog timers on built-in test (BIT) programs (e.g., power-on BIT)

Microcontrollers are associated with NAND flash memory for all its applications in AEH.

## 2.3.2 Foreseen Future Usage

The foreseen usage of microcontrollers in AEH revolves around an increasing complexity in the control and monitoring functions. The microcontrollers are already available and embedded in the chassis of avionics systems. They control temperature, power sequencing, and power distribution. For the monitoring function, foreseen use includes the capability to log data in the internal memory and communicate failure conditions with the external environment using hardware discrete signals.

The control function also comes into play when allowing external systems to connect and transfer of information between two remote systems. This growing functionality supports integrated diagnostics and remote fault management. The most common fault management strategy is to perform software-commanded resets. Microcontrollers perform this function.

In association with non-volatile memory storage, microcontrollers will take over the boot-loading capability and access control to data stored in memory for more complex applications than are currently used.

### 3. FEARED EVENTS AND FAILURE MODES OF EMBEDDED CONTROLLERS

As previously discussed in this task order, the following are the failure modes identified in the context of abstraction level, from the most abstract description to the least abstract:

- Functional abstraction level

- Logical abstraction level

- Physical abstraction level

The functional abstraction level contains both a system-level and a hardware-level transfer function representation. At this level, the microcontroller cannot be investigated independently from its intended function. The notion of usage domain is attached to an investigation at this abstraction level using the system-level transfer function. When considering the hardware-level transfer function, the focus of the failure mode identification is on the delivery of a coherent signal to the different software levels. Functional fault detection and mitigation means for the hardware-level transfer function viewpoint to cover the service provided by hardware to connected hardware or to software.

The logical abstraction level addresses the output of the microcontroller from its logical content viewpoint. This level is the most adapted to investigate failure modes of microcontrollers and to identify the possible fault detection and mitigation means.

At the physical level, the microcontroller's outputs are separated, and the signals are detailed down to the physical characteristics, including voltage, amperage, and timing. This abstraction level is too low to effectively describe the failure modes of a complex COTS microcontroller (e.g., because of the number of input/output pins). However, this level of abstraction is useful in particular cases, such as to characterize a failure mode identified at a higher level (e.g., bit stuck-at value, voltage oscillations, timing drift) or to estimate the effectiveness of detection/mitigation means (e.g., monitoring of a signal). This abstraction level is also typically used for faults caused by environmental factors, such as single-event effects, electromagnetic pulse, current, or voltage fluctuations.

Most of the literature addressing microcontrollers and compliance with safety requirements relates to the automobile industry and demonstration of compliance with ISO 26262 standard requirements [18]. The study of microcontrollers—even complex—is often limited to hardware-related issues, but there is a trend in the latest publications to consider software-related safety issues.

## 3.1 GLOBAL FAULT CLASSIFICATION

Faults are typically classified into two broad categories:

- Permanent faults

- Transient faults

The effects of permanent faults are non-reversible. Based on this consideration, aging effects can be included in the permanent fault category, whereas intermittent faults can be included in the transient fault category. Reference [19] considers specifically faults caused by electromagnetic interferences and adds the class of static faults: The pulse width is sufficient to deviate the microcontroller's state parameters from the rated values, but no abnormal behavior is observed at the system level.

Errors are classified in two categories:

- Soft errors can be recovered from, and typically with, a system restart.

- Hard errors require replacement of affected components.

Faults on a target system (e.g., microcontroller) can be investigated from three different levels:

- Hardware faults: covers the physical device, the logic, and the register-transfer level (RTL)

- Software faults: applies to operating system (OS) (kernel and middleware) and application

- Operation faults: covers faults committed by the user when interacting with the system

Furthermore, hardware faults can be tagged according to two categories of causal factors:

- Random hardware failures, which include faults caused by the environment